opt_ex14 : HiSIM_HV2 VDMOS Model Extraction

Requires: Utmost IV, SmartSpice, SmartView

Minimum Versions: Utmost IV 1.10.6.R, SmartSpice 4.17.1.C, SmartView 2.28.2.R

This example demonstrates how to extract a standard HiSIM_HV2 model parameters for a single geometry Vdmos device. The datasets used are two drain current versus gate voltage characteristics at the low and the high drain voltages and one drain current versus the drain voltage characteristic. In addition, the capacitance data such as Cg_sdb, Cg_sb and Cgd are included.

The following process parameters are defined in the model library. The tox value is fixed during the optimization.

- tox:Physical oxide thickness

- nsubc:Substrate impurity concentration

- nover:Impurity concentration of loverld at drain, and at source if cosym=1 and the value is declared

Also, the following model parameter values can be set to reasonable starting values. They are then optimized through the optimization sequence.

- loverld:Overlap length at drain side, and at source if cosym=1

- lovers:Overlap length at source side

- ldrift1:Length of light doped drift region at drain, and at source if cosym=1

- ldrift2:Length of heavily doped drift region at drain side, and at source if cosym=1

Note: The model flag cosym=0 is used.

Even though the Vdmos structure is different from the Ldmos, the drift region is only in the drain side similar to the Ldmos.

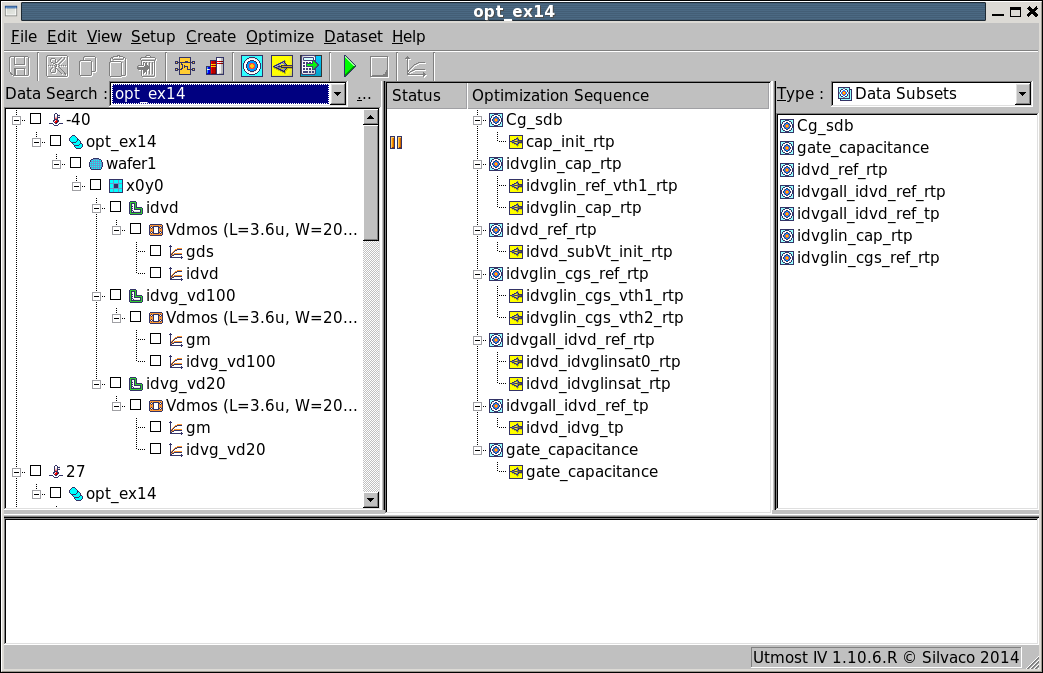

The project file opt_ex14.prj and the data file opt_ex14.uds for this example should be loaded into your database. When opened, the project will look as shown in opt_ex14_project.png .

The optimization sequence, which fully automates the extraction of HiSIM_HV2 model parameters, consists of seven sections. The section one is to get the initial estimate of the geometry correction terms. The section two extracts the threshold voltage region parameters. The third section is prepared to get the initial model parameters for the substrate current model. The section four aims to optimize the drift region resistance parameters at the low drain voltage. The bias dependency of the drift region resistance is optimized in the section five. And this completes the single geometry model parameters at the room temperature. The section six optimizes the temperature scaling model parameters to complete the HiSIM_HV2 DC model over the temperature change. The section seven is to get the gate capacitance characteristics.

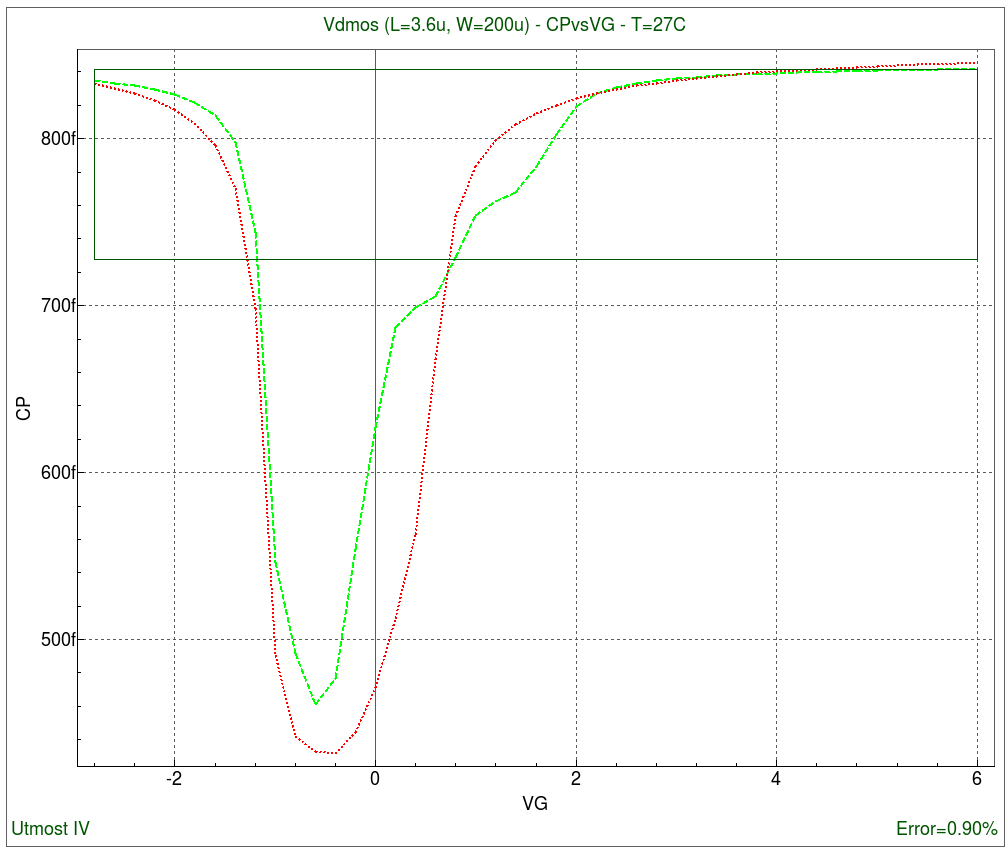

Section 1 : Cg_sdb

The first section is to estimate the drift region overlap length parameters and the channel width correction parameters of HiSIM_HV2 using the Cg_sdb (Cgg) capacitance characteristics. The following model parameters are extracted.

- loverld:Overlap length at drain side, and at source if cosym=1

- xldld:Gate overlap length at drain side

- xwd:Gate overlap width

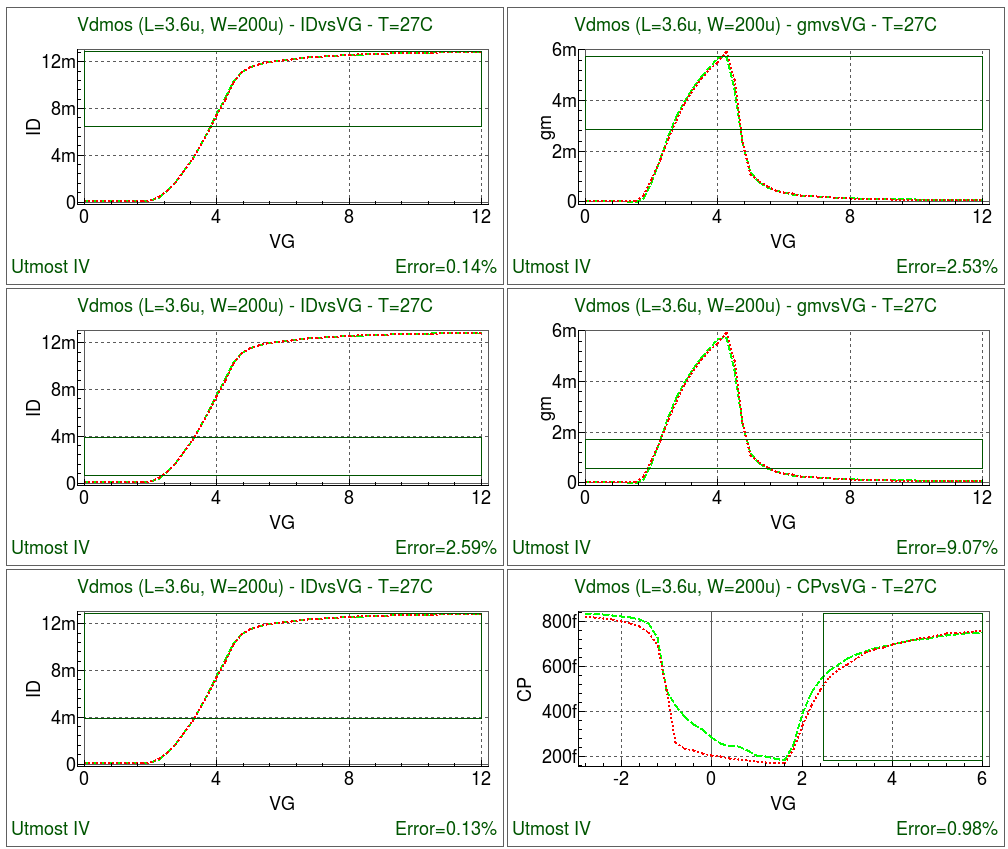

After this section has been completed, the fit to measured data will be as shown in opt_ex14_01.png .

Section 2 : idvglin_cap_rtp

This section extracts the fundamental parameters for the Vdmos device. The data sets in this section are the drain current versus the gate voltage characteristic at the low drain voltage and the cg_sdb and cg_sb capacitance characteristics at the room temperature. The following model parameters are extracted.

- nsubc:Substrate impurity concentration

- vfbc:Flat band voltage

- muecb0:Coulomb scattering

- muecb1:Coulomb scattering

- mueph0:Phonon scattering

- mueph1:Phonon scattering

- ndep:Depletion charge contribution on effective electric field

- ninv:Inversion charge contribution on effective electric field

- vfbover:Flat-band voltage in overlap region

- nover:Impurity concentration of loverld at drain, and at source if cosym=1 and the value is declared

- ldrift1:Length of light doped drift region at drain, and at source if cosym=1

- ldrift2:Length of heavily doped drift region at drain side, and at source if cosym=1

- rdrdjunc:Junction depth at channel/drift region for cordrift=1

- rdrmue:Field dependent mobility in drift region for cordrift=1

After this section has been completed, the fit to measured data will be as shown in opt_ex14_02.png .

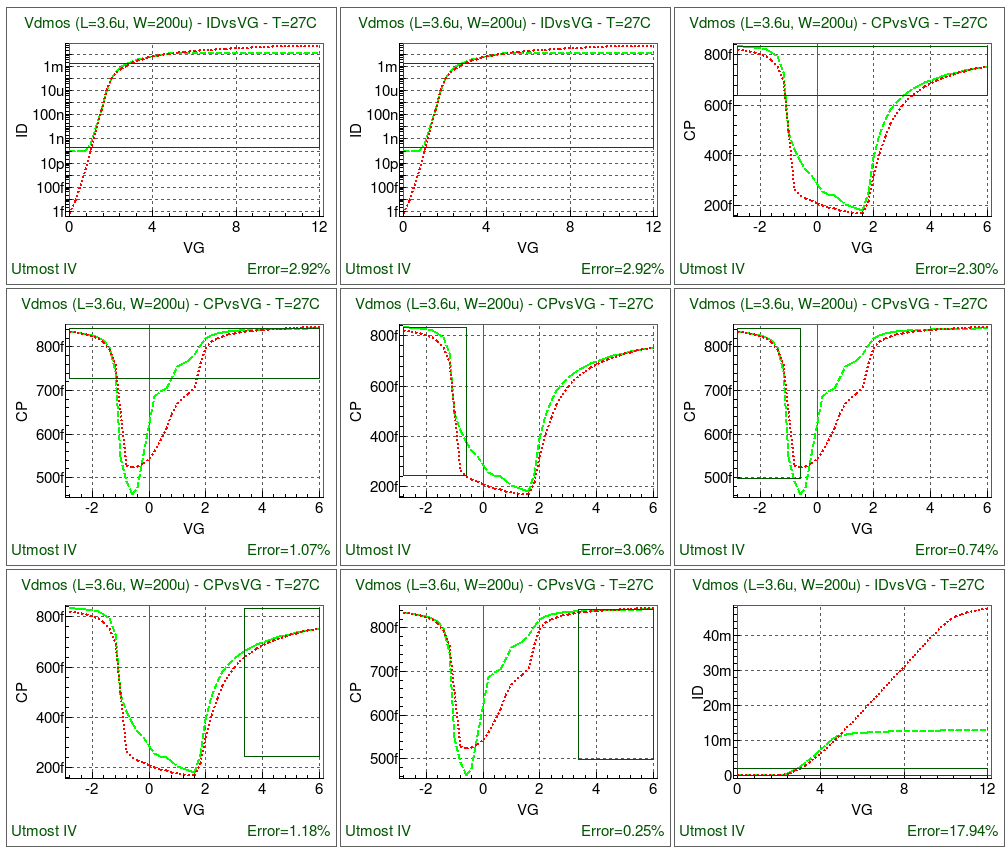

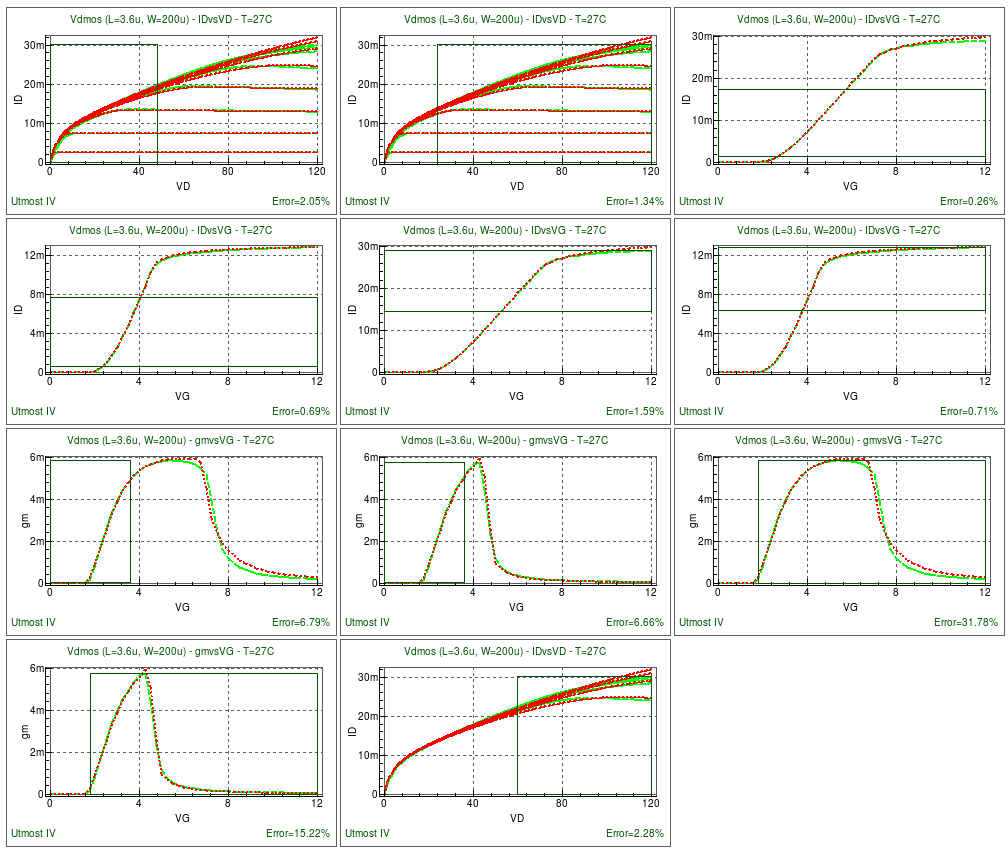

Section 3 : idvd_ref_rtp

The third section aims to obtain the initial values of the substrate current model and the channel length modulation parameters. The following model parameters are extracted.

- bb:High field mobility degradation

- sub1:Substrate current coefficient of magnitude

- sub2:Substrate current coefficient of exponential term

- svds:Substrate current coefficient of exponential term

- svgs:Substrate current dependence on vgs

- clm1:Hardness coefficient of channel/contact junction

- clm2:Coefficient of qb contribution

- clm3:Coefficient of qi contribution

- sc2:Vds dependence of short-channel effect

After this section has been completed, the fit to measured data will be as shown in opt_ex14_03.png .

Section 4 : idvglin_cgs_ref_rtp

This section extracts several parameters of the drift region resistance model. The data in this section is the drain current versus the gate voltage characteristic at the low drain voltage and the cg_sb capacitance versus the gate voltage. The cg_sb capacitance is used to observe the effect of the drift region resistance parameters. The following model parameters are extracted.

- rdrcx:Coefficient of current flow from xov for cordrift=1

- rdrdl1:Effective ldrift of current in drift region for cordrift=1

Also, the following model parameters used at the previous steps are included in this section to ensure the entire fitting.

- nsubc

- vfbc

- muecb0

- muecb1

- mueph0

- mueph1

- ninv

- ldrift1

- ldrift2

- rdrdjunc

- rdrmue

After this section has been completed, the fit to measured data will be as shown in opt_ex14_04.png .

Section 5 : idvgall_idvd_ref_rtp

The previous four sections concentrated mostly on the drain current versus the gate voltage at the low drain voltage. The intention was to get the precise threshold model parameters. Also, the model parameters of the drift region resistance at the low drain voltage was extracted as the initial values for the succeeding optimization steps. This section will use the drain current versus the drain voltage data in addition to the drain current versus the gate voltage at the low and the high drain voltages to optimize the saturation region parameters and the drift resistance dependency on the drain and the gate voltages. The gate capacitances of cg_sdb and cg_sb are included to see the parameter effects. The following model parameters are extracted.

- ninvd:Reduced resistance effect for small Vds

- vmax:Saturation velocity

- vover:Velocity overshoot effect

- rdrcar:High field injection in drift region for cordrift=1

- rdrqover:Inclusion of the overlap change in rdrift for cordrift=1

- rdrvmax:Saturation velocity in drift region for cordrift=1

- rdrbb:High field mobility in drift region

- rth0:Thermal resistance

- subld1:Substrate current induced in ldrift model

- subld2:Substrate current induced in ldrift model

Also, the following model parameters used at the previous steps are included in this section to ensure the entire fitting.

- muecb0

- muecb1

- mueph0

- mueph1

- bb

- ninv

- ldrift1

- ldrift2

- rdrcx

- rdrdl1

- rdrdjunc

- rdrmue

- sub1

- sub2

- svds

- svgs

After this section has been completed, the fit to measured data will be as shown in opt_ex14_05.png .

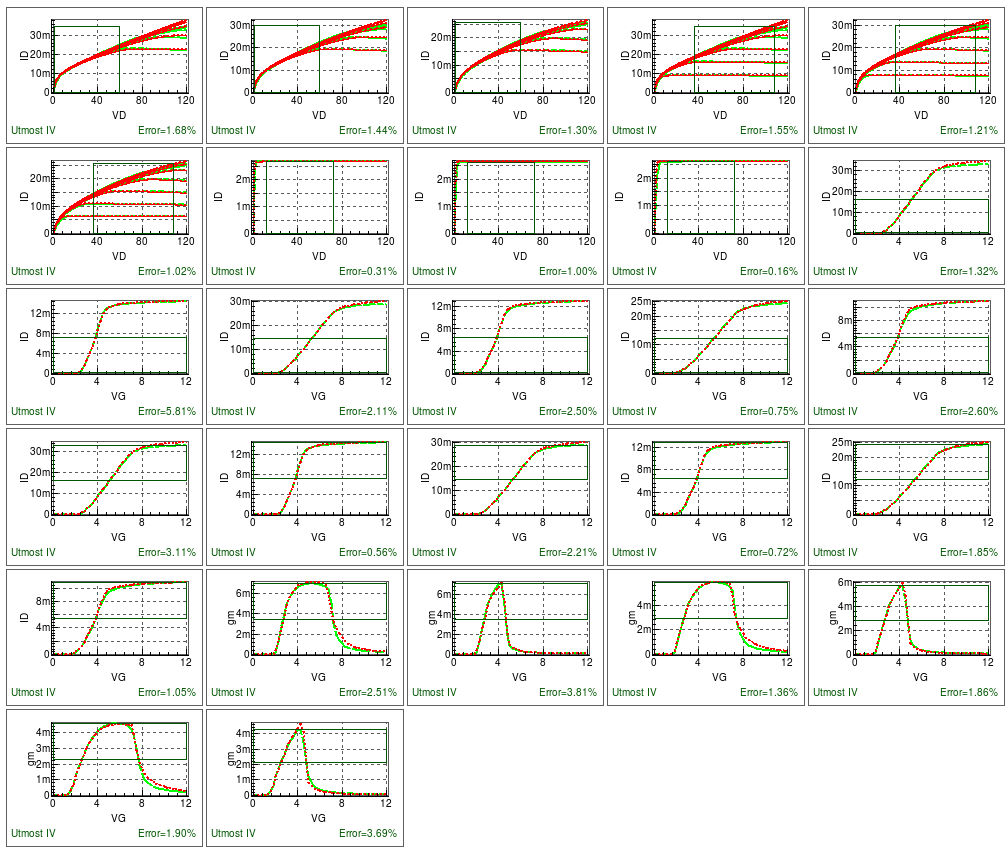

Section 6: idvgall_idvd_ref_tp

This section extracts the temperature model parameters using both the drain current versus the gate voltage and the drain current versus the drain voltage characteristics at three temperatures. The following model parameters are extracted.

- bgtmp1:Temperature dependence of bandgap

- bgtmp2:Temperature dependence of bandgap

- muetmp:Temperature dependence of phonon scattering

- vmaxt1:Temperature dependence of velocity

- vmaxt2:Temperature dependence of velocity

- vtmp:Temperature dependence of the saturation velocity

- rdrmuetmp:Temperature dependence of resistance for cordrift=1

- rdrvtmp:Temperature dependence of resistance for cordrift=1

- rthtemp1:Temperature dependence of thermal resistance

- rthtemp2:Temperature dependence of thermal resistance

Also, the following model parameters used at the previous steps are included in this section to ensure the entire fitting.

- bb

- rdrbb

After this section has been completed, the fit to measured data will be as shown in opt_ex14_06.png .

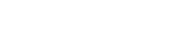

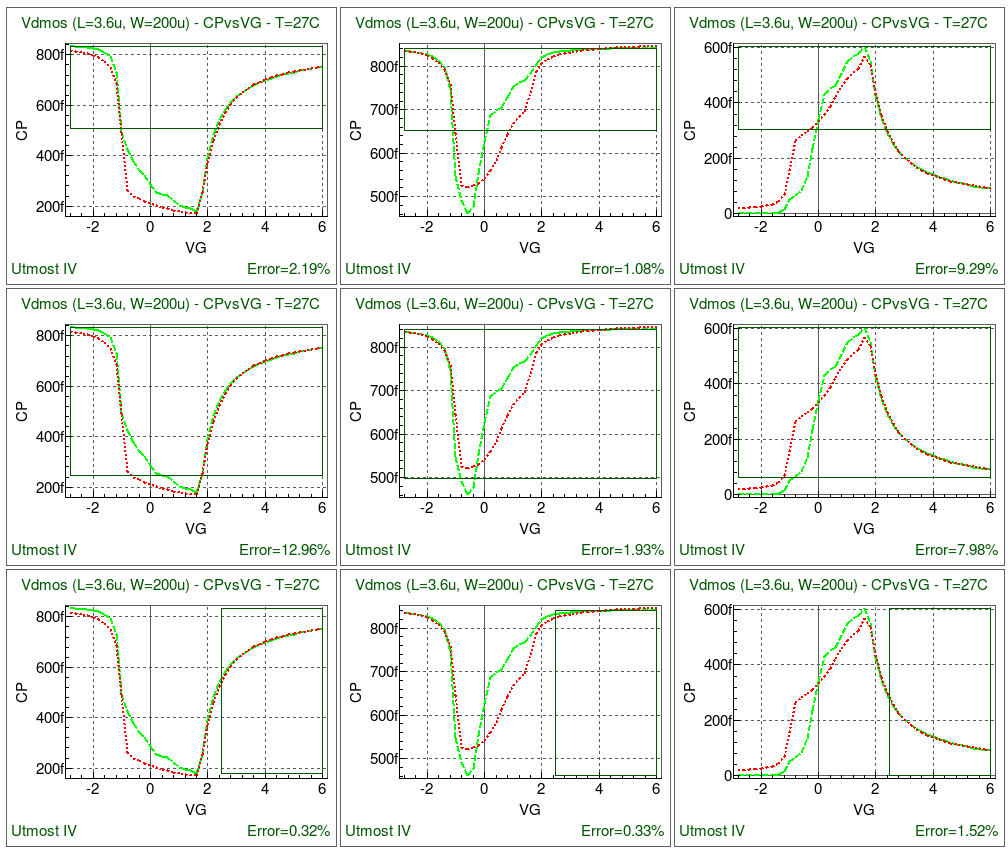

Section 7 : gate_capacitance

This section is to finalize the gate capacitance characteristic fitting. The following model parameters are extracted.

- xwdc:Gate overlap in width for capacitance calculation

- cvdsover:Parameter for cgg for vds =! 0

- cgso:Gate-to-source overlap capacitance

- cgdo:Gate-to-drain overlap capacitance

The parameters used in the previous section are the following;

- vfbover

- loverld

After this section has been completed, the fit to measured data will be as shown in opt_ex14_07.png .

The sequence is prepared for the best fit. No repeated run would be necessary. When complete, the model card can be exported into an external model library file as shown in the output file opt_ex14.lib.

Note for reducing the run time.

Utmost IV is able to control the number of parallel runs of SmartSpice. The increase of number of smartspice shortens the run time for the multi-core machines. Edit -> Preferences -> Simulator

opt_ex14.lib

.MODEL HiSIM_HV2 NMOS ( +LEVEL = 73 VERSION = 2.1 coovlp = 1 +coovlps = 1 coisub = 1 coiigs = 0 +cogidl = 0 coisti = 0 coadov = 1 +conqs = 0 corg = 0 corbnet = 0 +coflick = 0 cothrml = 0 coign = 0 +coiprv = 1 copprv = 1 codfm = 0 +coselfheat = 1 +cotemp = 0 +cosubnode = 0 +cosym = 0 cordrift = 1 coqovsm = 1 +coerrrep = 1 eg0 = 1.1785 bgtmp1 = 0.000247366 +bgtmp2 = -3.71827e-07 muetmp = 1.73405 tnom = 27 +vtmp = 0.323045 vmaxt1 = 0.000444372 vmaxt2 = -7.96278e-07 +ninvdt1 = 0 ninvdt2 = 0 rthtemp1 = 4.53052e-05 +rthtemp2 = 0 tox = 6e-08 xl = 0 +xw = 0 xld = 0 xldld = 1.23026e-06 +xwd = 1.09086e-07 xwdld = 0 xwdc = -1e-08 +tpoly = 2e-07 ll = 0 lld = 0 +lln = 0 wl = 0 wld = 0 +wln = 0 nsubc = 4.69752e+16 nsubp = 1e+18 +nsubsub = 1e+15 lp = 0 npext = 5e+17 +lpext = 1e-50 vfbc = -1.12589 vbi = 1.1 +kappa = 3.9 ldrift1 = 1.27682e-07 ldrift2 = 1.30081e-07 +ldrift1s = 0 ldrift2s = 1e-06 ddrift = 1e-06 +loverld = 4.82849e-06 lovers = 5e-08 vbsmin = -10.5 +vgsmin = -100 muecb0 = 100 muecb1 = 3645.09 +mueph0 = 0.25 mueph1 = 30000 muephl = 0 +mueplp = 1 muesr0 = 2 muesr1 = 8e+15 +muesrl = 0 mueslp = 1 ndep = 0.560727 +ndepl = 0 ndeplp = 1 ninv = 0.00976814 +ninvd = 0 ninvdw = 0 ninvdwp = 1 +bb = 1.82222 vmax = 1.00668e+07 vover = 0.302982 +voverp = 0.3 rsh = 0 rshg = 0 +rbpb = 50 rbpd = 50 rbps = 50 +rbdb = 50 rbsb = 50 rdrdl1 = 1.9985e-06 +rdrdl2 = 0 rdrcx = 0.283434 rdrcar = 5.37034e-09 +rdrdjunc = 5.44849e-07 rdrmue = 100 rdrvmax = 3.18072e+07 +rdrvmaxl = 0 +rdrvmaxlp = 1 +rdrvmaxw = 0 +rdrvmaxwp = 1 +rdrmuel = 0 rdrmuelp = 1 rdrbb = 0.957247 +rdrqover = 2804.71 rdrvtmp = -0.218072 +rdrmuetmp = 1.60286 +gbmin = 1e-12 rth0 = 0.303333 cth0 = 1e-07 +rth0w = 0 rth0wp = 1 rth0nf = 0 +powrat = 1 +prattemp1 = 0 +prattemp2 = 0 +shemax = 500 nfalp = 1e-19 nftrp = 1e+10 +cit = 0 falph = 1 sub1 = 0.001 +sub1l = 0.0025 sub1lp = 1 sub2 = 250 +sub2l = 2e-06 svds = 0.2 slg = 3e-08 +slgl = 0 slglp = 1 svbs = 0.5 +svbsl = 0 svbslp = 1 svgs = 0.7 +svgsl = 0 svgslp = 1 svgsw = 0 +svgswp = 1 ibpc1 = 0 ibpc2 = 0 +ibpc1l = 0 ibpc1lp = -1 subld1 = 9.51834e-06 +subld2 = 2.91716e-09 subld1l = 0 subld1lp = 1 +xpdv = 0 xpvdth = 0 xpvdthg = 0 +mphdfm = -0.3 parl2 = 1e-08 sc1 = 0 +sc2 = 0 sc3 = 0 sc4 = 0 +scp1 = 0 scp2 = 0 scp3 = 0 +scp21 = 0 bs1 = 0 bs2 = 0.9 +clm1 = 0.0100504 clm2 = 3.99949 clm3 = 4.99987 +clm5 = 1 clm6 = 0 wfc = 0 +wvth0 = 0 nsubcw = 0 nsubcwp = 1 +nsubp0 = 0 nsubwp = 1 muephw = 0 +muepwp = 1 muesrw = 0 mueswp = 1 +vthsti = 0 vdsti = 0 scsti1 = 0 +scsti2 = 0 nsti = 1e+16 wsti = 0 +wstil = 0 wstilp = 1 wstiw = 0 +wstiwp = 1 wl1 = 0 wl1p = 1 +nsubpsti1 = 0 +nsubpsti2 = 0 +nsubpsti3 = 1 +muesti1 = 0 muesti2 = 0 muesti3 = 1 +saref = 1e-06 sbref = 1e-06 wl2 = 0 +wl2p = 1 muephs = 0 muepsp = 1 +vovers = 0 voversp = 0 qme1 = 0 +qme2 = 2 qme3 = 0 pgd1 = 0 +pgd2 = 1 pgd4 = 0 gleak1 = 50 +gleak2 = 1e+07 gleak3 = 0.06 gleak4 = 4 +gleak5 = 7500 gleak6 = 0.25 gleak7 = 1e-06 +egig = 0 igtemp2 = 0 igtemp3 = 0 +glksd1 = 1e-15 glksd2 = 1000 glksd3 = -1000 +glkb1 = 5e-16 glkb2 = 1 glkb3 = 0 +glpart1 = 0.5 fn1 = 50 fn2 = 0.00017 +fn3 = 0 fvbs = 0.012 gidl1 = 2 +gidl2 = 3e+07 gidl3 = 0.9 gidl4 = 0 +gidl5 = 0.2 vzadd0 = 0.01 pzadd0 = 0.005 +ddltmax = 10 ddltslp = 0 ddltict = 10 +js0 = 5e-07 js0sw = 0 nj = 1 +njsw = 1 xti = 2 xti2 = 0 +divx = 0 ctemp = 0 cisb = 0 +cisbk = 0 cvb = 0 cj = 0.0005 +cjsw = 5e-10 cjswg = 5e-10 mj = 0.5 +mjsw = 0.33 mjswg = 0.33 pb = 1 +pbsw = 1 pbswg = 1 vdiffj = 0.0006 +tcjbd = 0 tcjbdsw = 0 tcjbdswg = 0 +tcjbs = 0 tcjbssw = 0 tcjbsswg = 0 +xqy = 0 xqy1 = 0 xqy2 = 2 +nover = 1.95762e+16 vfbover = -0.993669 qovadd = 0 +novers = 1e+16 ovslp = 2.1e-07 ovmag = 0.6 +cgso = 2.34797e-11 cgdo = 1.8984e-11 cgbo = 0 +cvdsover = 0.0475194 dly1 = 1e-10 dly2 = 0.7 +dly3 = 8e-07 pt2 = 0 pt4 = 0 +pt4p = 1 ptl = 0 ptlp = 1 +ptp = 3.5 gdl = 0 gdld = 0 +gdlp = 0 gdsleak = 0 lbinn = 1 +wbinn = 1 lmax = 1 lmin = 0 +wmax = 1 wmin = 0 )

opt_ex14.uds