001_biaschk : Biascheck functionality

Requires: SmartSpice & Smartview

Minimum Versions: SMARTSPICE 3.16.12.R

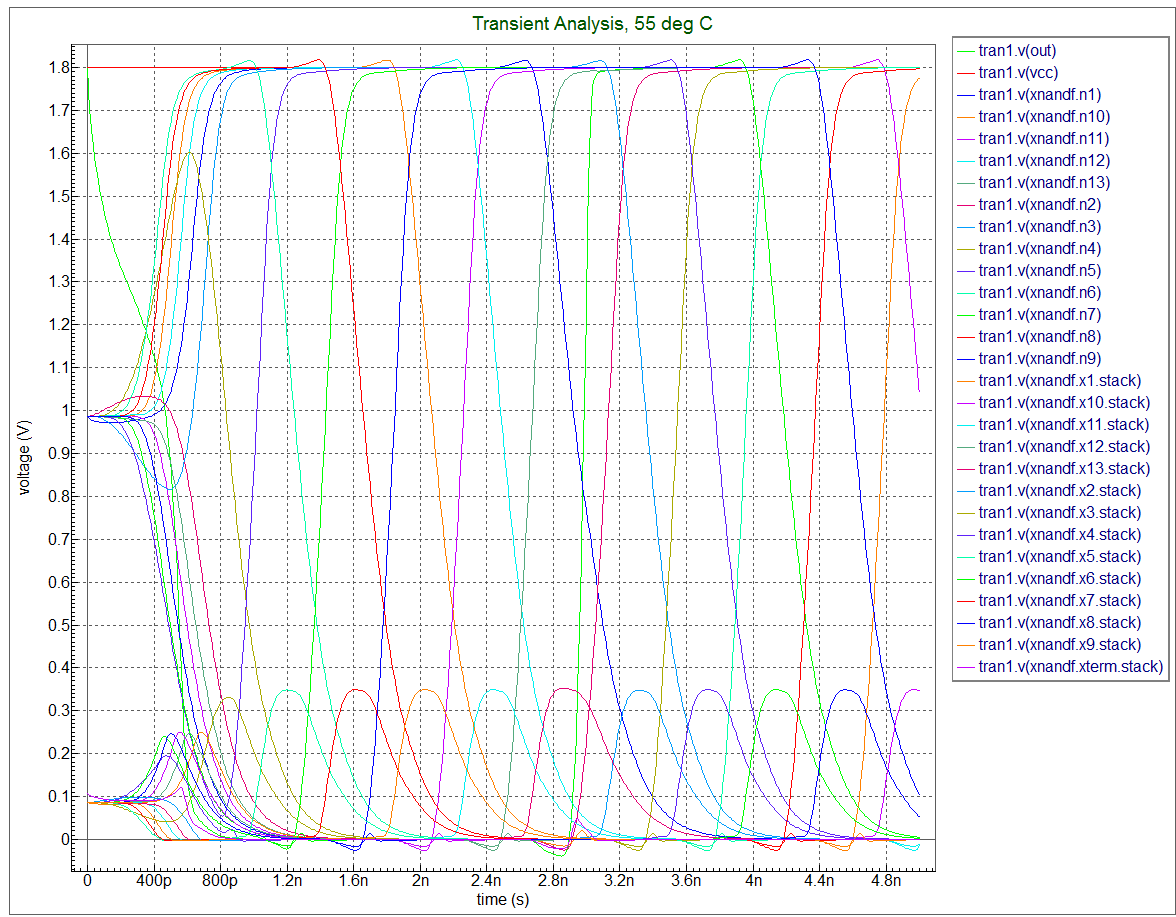

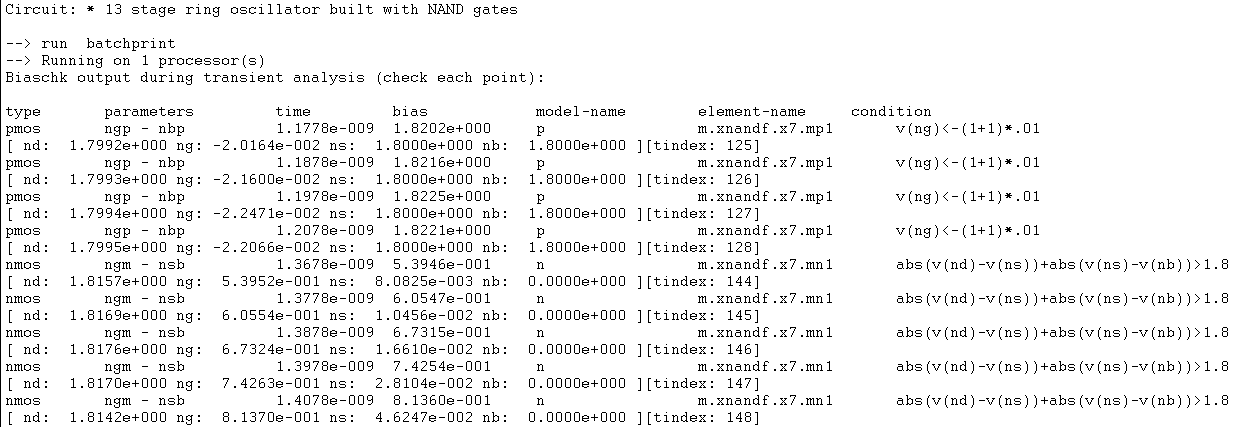

A 13 stage ring Oscillator built with fictional BSIM4 models is used to show how you can setup the .BIASCHK functionality to monitor a differential potential across the MOS devices in the circuit to compare to a fixed value and report when this value is exceeded. The input deck has these 2 important seup lines:

- .biaschk NMOS detailed condition = "ABS(V(nd)-V(ns))+ABS(V(ns)-V(nb))>1.8" terminal1=ngm terminal2=nsb limit=0.5 noise=0.01 name=m.xnandf.x7.mn1

- .biaschk PMOS detailed condition="v(ng) < -(1+1)*.01" terminal1=ngp terminal2=nbp limit=0.5 noise=0.01 name=m.xnandf.x7.mp1

to setup checking of the NMOS and PMOS device conditions.

The output set of waveforms look like this plot and in the output log you can see the reported details where this condition has been exceeeded in amplitude and time during the transient simulation.

You can use this as a template to check devices in your particular circuit to make sure devices are exposed to right voltages and these conditions are not exceeded as this will affect the reliability of your circuit.

biaschk_cond_mos.in

* 13 stage ring oscillator built with NAND gates *************************************************** .options nomod brief nodeck .options gmin=1e-12 .option temp=55 .global Vcc Vc Vcc 0 DC 1.8 XnandF out XnandF_13 .tran 3ps 5ns 0 10ps .save all(v) *.let nmospar= 'ABS(V(nd)-V(ns))+ABS(V(ns)-V(nb))' *.let nmospar='m.xnandf.x7.mn1[d]' .IC V(out)=1.8 .option biaschkmode=1 .biaschk NMOS detailed condition = "ABS(V(nd)-V(ns))+ABS(V(ns)-V(nb))>1.8" terminal1=ngm terminal2=nsb limit=0.5 noise=0.01 name=m.xnandf.x7.mn1 .biaschk PMOS detailed condition="v(ng) < -(1+1)*.01" terminal1=ngp terminal2=nbp limit=0.5 noise=0.01 name=m.xnandf.x7.mp1 ***************oscil. wired up***** .subckt XnandF_13 float X1 N1 N2 XstgNAND X2 N2 N3 XstgNAND X3 N3 N4 XstgNAND X4 N4 N5 XstgNAND X5 N5 N6 XstgNAND X6 N6 N7 XstgNAND X7 N7 N8 XstgNAND X8 N8 N9 XstgNAND X9 N9 N10 XstgNAND X10 N10 N11 XstgNAND X11 N11 N12 XstgNAND X12 N12 N13 XstgNAND X13 N13 N1 XstgNAND Xterm N1 float XstgNAND C1 N1 0 0.05e-12 C2 N2 0 0.05e-12 C3 N3 0 0.05e-12 C4 N4 0 0.05e-12 C5 N5 0 0.05e-12 C6 N6 0 0.05e-12 C7 N7 0 0.05e-12 C8 N8 0 0.05e-12 C9 N9 0 0.05e-12 C10 N10 0 0.05e-12 C11 N11 0 0.05e-12 C12 N12 0 0.05e-12 C13 N13 0 0.05e-12 .ends .subckt XstgNAND in out Mn1 out in Stack N W=1.5u L=0.14u AD=0.75p PD=4u AS=0.54p PS=2.22u Mn2 Stack Vcc 0 N W=1.5u L=0.14u AD=0 PD=0 Mp1 out in Vcc P W=2.25u L=0.14u AD=0.4p PD=2.61u Mp2 out Vcc Vcc P W=2.25u L=0.14u AD=0.4p PD=2.61u .ends ******** BSIM4 Fictional Model Card for NMOS ******** .MODEL N NMOS LEVEL=14 VERSION=2.1 DRDELTA=0.05 TNOM=27 BULK=0 + EPSROX=3.9 TOXE=3e-9 TOXP=3e-9 TOXM=3e-9 TOXREF=3e-9 DTOX=0 + MOBMOD=0 RDSMOD=0 IGCMOD=1 IGBMOD=1 DIOMOD=1 CAPMOD=2 + RGATEMOD=3 RBODYMOD=1 TRNQSMOD=0 ACNQSMOD=0 FNOIMOD=1 + TNOIMOD=0 PERMOD=1 GEOMOD=1 PARAMCHK=0 BINUNIT=1 + NDEP=1.7e17 NGATE=9e19 VTH0=0.42 PHIN=0 XJ=9e-8 NSD=1e20 + VFB=-0.76 K1=0.33 K2=-1.87e-2 K3=80 K3b=0 W0=2.5e-6 KT1=-0.11 + KT1L=0 KT2=2.2e-2 LPE0=5.75e-8 LPEB=2.3e-10 DVT0=2.89 DVT1=0.53 + DVT2=-3.2e-2 DVT0W=0 DVT1W=0 DVT2W=0 DVTP0=7.32e-7 DVTP1=0.12 + DSUB=0.058 ETA0=0.001 ETAB=0 + CDSC=2.58e-4 CDSCD=6.1e-8 CDSCB=0 CIT=0 NFACTOR=1.1 VOFF=-0.02 VOFFL=0 + MINV=0.05 VSAT=9.2e4 AT=3.3e4 U0=4.19e-2 UA=8.7e-16 UB=3.06e-18 + UC=4.6e-13 UTE=-1.5 UA1=4.31e-9 UB1=7.61e-18 UC1=-5.6e-11 + RDSW=369.4 RDW=184.7 RSW=184.7 PRWG=3.22e-8 PRWB=6.8e-11 WR=1 + RDSWMIN=0 RDWMIN=0 RSWMIN=0 PRT=0 A0=1.1 AGS=1e-20 B0=-1e-20 + B1=0 KETA=-0.047 A1=0 A2=1 DELTA=0.014 PVAG=1e-20 PCLM=6.28e-4 + PDITS=0.2 PDITSL=2.3e6 PDITSD=0.23 FPROUT=0.2 PDIBLCB=3.4e-8 + PDIBLC1=0.81 DROUT=0.56 PDIBLC2=9.84e-06 PSCBE1=8.14e8 PSCBE2=9.58e-07 + LINT=5e-9 WINT=5e-9 DWG=0 DWB=0 WL=0 WW=0 WWL=0 + WLN=1 WWN=1 LL=0 LW=0 LWL=0 LLN=1 LWN=1 + XGW=3e-7 XGL=4e-8 NGCON=1 RSHG=0.4 XRCRG1=12 XRCRG2=5 + DMCG=5e-6 DMCI=5e-6 DMDG=5e-6 DMCGT=6e-7 DWJ=4.5e-8 RSH=6 + RBDB=15 RBPD=15 RBSB=15 RBPS=15 RBPB=5 GBMIN=1e-10 + CGSO=7.43e-10 CGDO=7.43e-10 CGBO=2.56e-11 CGSL=1e-14 CGDL=1e-14 + CKAPPAS=0.5 CKAPPAD=0.5 NOFF=0.9 VOFFCV=0.02 ACDE=1 MOIN=15 XPART=0 + JSS=1e-4 JSWS=1e-11 JSWGS=1e-10 CJS=5e-4 CJSWS=5e-10 CJSWGS=3e-10 + PBS=1 PBSWS=1 PBSWGS=1 NJS=1 XTIS=3 MJS=0.5 MJSWS=0.33 MJSWGS=0.33 + XJBVS=1 BVS=10 IJTHSFWD=1e-2 IJTHSREV=1e-3 + JSD=1e-4 JSWD=1e-11 JSWGD=1e-10 CJD=5e-4 CJSWD=5e-10 CJSWGD=5e-10 + PBD=1 PBSWD=1 PBSWGD=1 NJD=1 XTID=3 MJD=0.5 MJSWD=0.33 MJSWGD=0.33 + XJBVD=1 BVD=10 IJTHDFWD=1e-2 IJTHDREV=1e-3 + TCJ=1e-3 TCJSW=1e-3 TCJSWG=1e-3 TPB=0.005 TPBSW=0.005 TPBSWG=0.005 + ALPHA0=7.4e-2 ALPHA1=0.005 BETA0=30 AGIDL=2e-4 BGIDL=2.1e9 CGIDL=2e-4 + EGIDL=0.8 AIGC=0.043 BIGC=0.0054 CIGC=0.0075 AIGSD=0.043 BIGSD=0.0054 + CIGSD=0.0075 DLCIG=2.2e-8 AIGBACC=0.043 BIGBACC=0.0054 CIGBACC=0.0075 + AIGBINV=0.35 BIGBINV=0.03 CIGBINV=0.006 NIGC=1 NIGBACC=1 NIGBINV=3 + NTOX=1 EIGBINV=1.1 PIGCD=1.0 POXEDGE=1 ******** BSIM4 Fictional Model Card for PMOS ******** .MODEL P PMOS LEVEL=14 VERSION=2.1 DRDELTA=0.05 TNOM=27 BULK=Vcc + EPSROX=3.9 TOXE=3e-9 TOXP=3e-9 TOXM=3e-9 TOXREF=3e-9 DTOX=0 + MOBMOD=0 RDSMOD=0 IGCMOD=1 IGBMOD=1 DIOMOD=1 CAPMOD=2 + RGATEMOD=1 RBODYMOD=1 TRNQSMOD=1 ACNQSMOD=0 FNOIMOD=1 + TNOIMOD=0 PERMOD=1 GEOMOD=1 PARAMCHK=0 BINUNIT=1 + NDEP=1.7e17 NGATE=9e19 VTH0=-0.42 PHIN=0 XJ=9e-8 NSD=1e20 + VFB=0.76 K1=0.33 K2=-1.87e-2 K3=80 K3b=0 W0=2.5e-6 KT1=-0.11 + KT1L=0 KT2=2.2e-2 LPE0=5.75e-8 LPEB=2.3e-10 DVT0=2.89 DVT1=0.53 + DVT2=-3.2e-2 DVT0W=0 DVT1W=0 DVT2W=0 DVTP0=7.32e-7 DVTP1=0.12 + DSUB=0.058 ETA0=0.001 ETAB=0 + CDSC=2.58e-4 CDSCD=6.1e-8 CDSCB=0 CIT=0 NFACTOR=1.1 VOFF=-0.02 VOFFL=0 + MINV=0.05 VSAT=9.2e4 AT=3.3e4 U0=4.19e-2 UA=8.7e-16 UB=3.06e-18 + UC=4.6e-13 UTE=-1.5 UA1=4.31e-9 UB1=7.61e-18 UC1=-5.6e-11 + RDSW=369.4 RDW=184.7 RSW=184.7 PRWG=3.22e-8 PRWB=6.8e-11 WR=1 + RDSWMIN=0 RDWMIN=0 RSWMIN=0 PRT=0 A0=1.1 AGS=1e-20 B0=-1e-20 + B1=0 KETA=-0.047 A1=0 A2=1 DELTA=0.014 PVAG=1e-20 PCLM=6.28e-4 + PDITS=0.2 PDITSL=2.3e6 PDITSD=0.23 FPROUT=0.2 PDIBLCB=3.4e-8 + PDIBLC1=0.81 DROUT=0.56 PDIBLC2=9.84e-06 PSCBE1=8.14e8 PSCBE2=9.58e-07 + LINT=5e-9 WINT=5e-9 DWG=0 DWB=0 WL=0 WW=0 WWL=0 + WLN=1 WWN=1 LL=0 LW=0 LWL=0 LLN=1 LWN=1 + XGW=3e-7 XGL=4e-8 NGCON=1 RSHG=0.4 XRCRG1=12 XRCRG2=5 + DMCG=5e-6 DMCI=5e-6 DMDG=5e-6 DMCGT=6e-7 DWJ=4.5e-8 RSH=6 + RBDB=15 RBPD=15 RBSB=15 RBPS=15 RBPB=5 GBMIN=1e-10 + CGSO=7.43e-10 CGDO=7.43e-10 CGBO=2.56e-11 CGSL=1e-14 CGDL=1e-14 + CKAPPAS=0.5 CKAPPAD=0.5 NOFF=0.9 VOFFCV=0.02 ACDE=1 MOIN=15 XPART=0 + JSS=1e-4 JSWS=1e-11 JSWGS=1e-10 CJS=5e-4 CJSWS=5e-10 CJSWGS=3e-10 + PBS=1 PBSWS=1 PBSWGS=1 NJS=1 XTIS=3 MJS=0.5 MJSWS=0.33 MJSWGS=0.33 + XJBVS=1 BVS=10 IJTHSFWD=1e-2 IJTHSREV=1e-3 + JSD=1e-4 JSWD=1e-11 JSWGD=1e-10 CJD=5e-4 CJSWD=5e-10 CJSWGD=5e-10 + PBD=1 PBSWD=1 PBSWGD=1 NJD=1 XTID=3 MJD=0.5 MJSWD=0.33 MJSWGD=0.33 + XJBVD=1 BVD=10 IJTHDFWD=1e-2 IJTHDREV=1e-3 + TCJ=1e-3 TCJSW=1e-3 TCJSWG=1e-3 TPB=0.005 TPBSW=0.005 TPBSWG=0.005 + ALPHA0=7.4e-2 ALPHA1=0.005 BETA0=30 AGIDL=2e-4 BGIDL=2.1e9 CGIDL=2e-4 + EGIDL=0.8 AIGC=0.043 BIGC=0.0054 CIGC=0.0075 AIGSD=0.043 BIGSD=0.0054 + CIGSD=0.0075 DLCIG=2.2e-8 AIGBACC=0.043 BIGBACC=0.0054 CIGBACC=0.0075 + AIGBINV=0.35 BIGBINV=0.03 CIGBINV=0.006 NIGC=1 NIGBACC=1 NIGBINV=3 + NTOX=1 EIGBINV=1.1 PIGCD=1.0 POXEDGE=1 .end

001_biaschk

[an error occurred while processing this directive]