004 : Parallel/Series Merge and Reduction of Devices

Minimum Required Versions: Expert 4.10.37.R, Guardian LVS 4.8.36.R

1. Merge/Reduction

The number of devices and the connection order might be different between the schematic and the layout in the following cases.

- A gate width is increased by connecting several MOS devices in parallel.

- One device in the schematic is composed of several devices in the layout.

- The connection of the MOS devices forming a logic gate is different in the schematic and the layout.

The degree of freedom of the comparison can be improved by merging and reducing these devices.

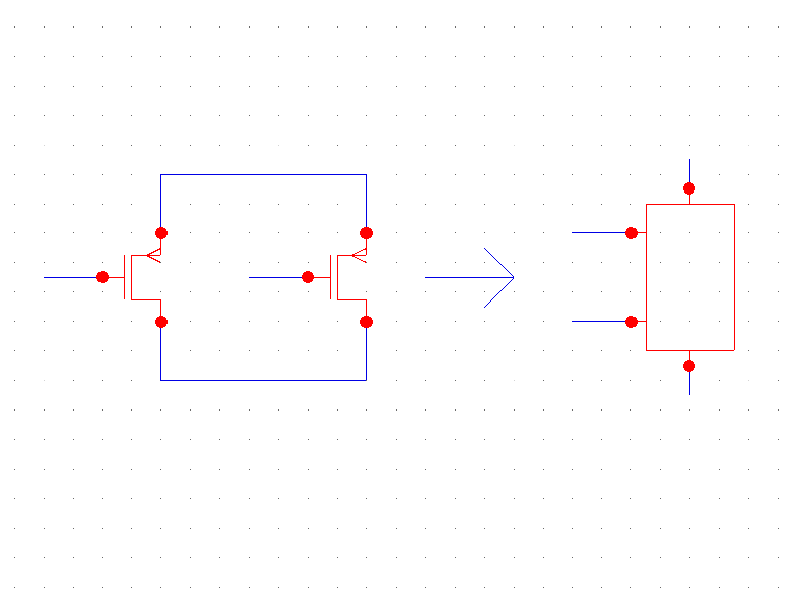

2. Parallel Merge

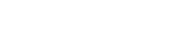

The Parallel merge option merges devices of the same type that are connected in parallel into one element, regardless of the number of terminals (see par_mer.png

).

3. Series Merge

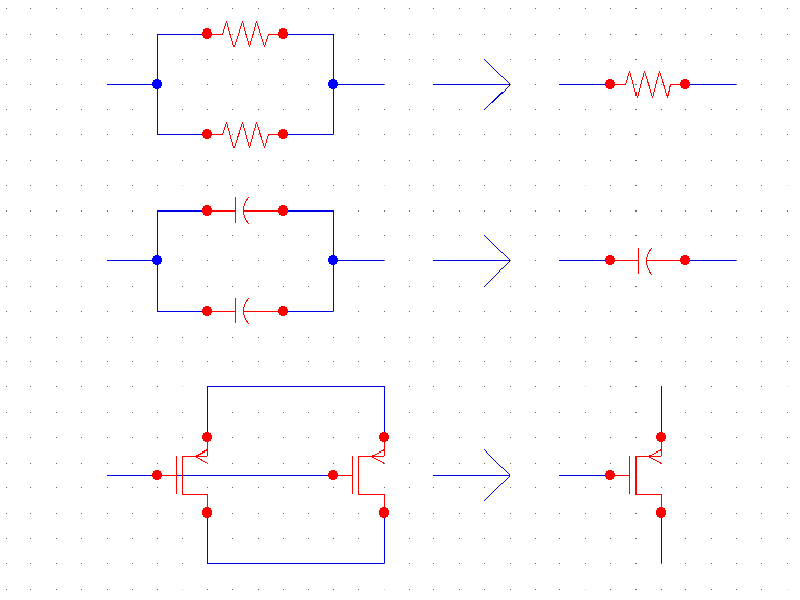

3.1. Passive Element Series Merge

The Series merge option merges devices of the same type that are connected in series into a single element. A pair of terminal devices must be connected to the same net in order to merge into one element (see ser_mer_pas.png

).

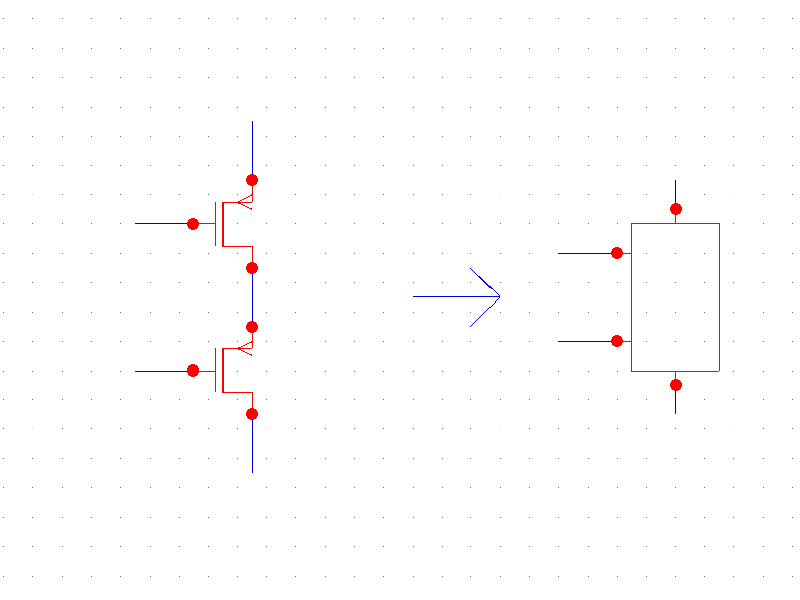

3.2. MOS, JFET and MESFET Series Merge

MOS, JFET, and MESFET devices with a common gate, and connected by their source/drain, can be merged into one element (see ser_mer.png

).

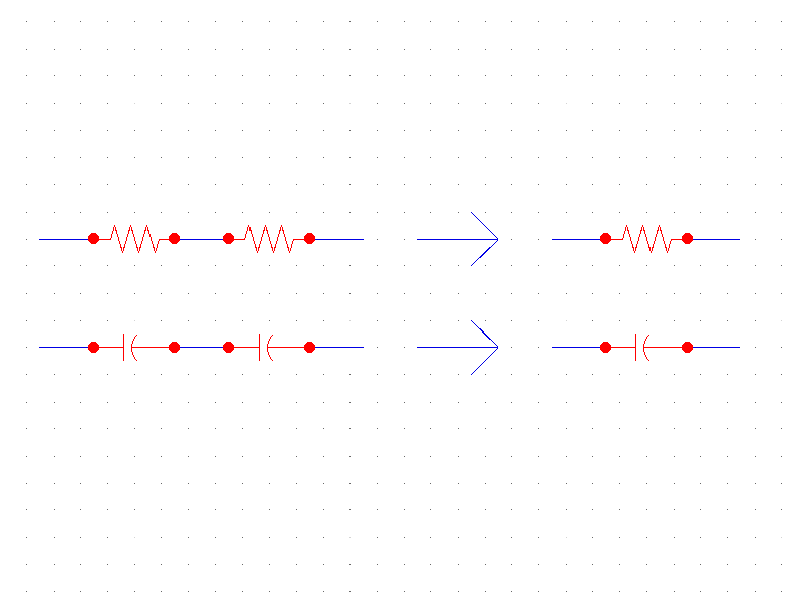

4. MOS, JFET, MESFET and Bipolar Parallel Reduction

The MOS, JFET, MESFET and Bipolar Parallel reduction option reduces the same type MOS, JFET, MESFET or bipolar transistors to a single element if they are connected in parallel with different gate (base) terminals. Once they are reduced, the resulting device will have swappable gate (base) terminals (see par_red.png

).

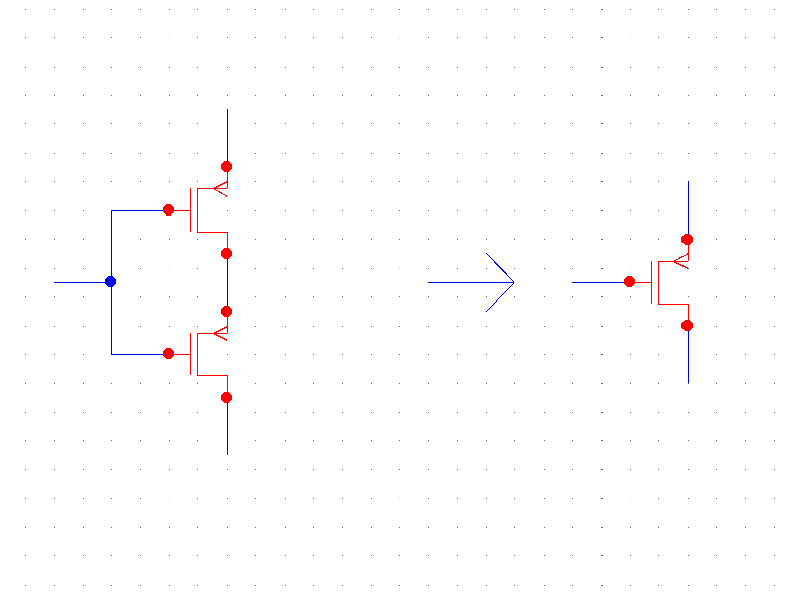

5. MOS, JFET, MESFET and Bipolar Series Reduction

The MOS, JFET, MESFET and Bipolar Series reduction option reduces the same type MOS, JFET, MESFET or bipolar transistors to a single element if they are connected in series with different gate (base) terminals. Once they are reduced, the resulting device will have swappable gate (base) terminals (see ser_red.png

).

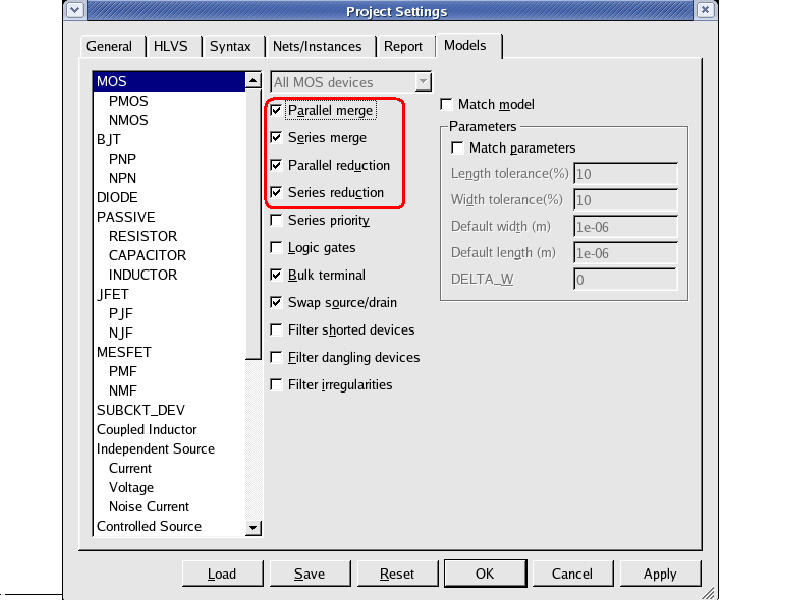

6. Setting of Merge/Reduction

Merge/reduction is set in the Models tab in the Project Settings dialog (see project_settings.png

).

7. Execution of Parallel Merge

1) Launch Guardian LVS from Expert by selecting Verification->LVS->Launch LVS .

2) Load par_mer.gpr by clicking the Load button at the bottom of the Project Settings dialog.

3) Run LVS.

4) Check the LVS result. The netlists are NOT EQUIVALENT message will be displayed in the LVS log.

5) Turn on the Parallel merge option in the Models tab, and run LVS.

6) Check the LVS result. The message netlists are EQUIVALENT will be displayed.

8. Execution of Series Merge

1) Launch Guardian LVS .

2) Load ser_mer.gpr .

3) Run LVS.

4) Check the LVS result. The message netlists are NOT EQUIVALENT will be displayed.

5) Turn on the Series merge option in the Models tab, and run LVS.

6) Check the LVS result. The message netlists are EQUIVALENT will be displayed.

9. Execution of Parallel/Series Reduction

1) Launch Guardian LVS .

2) Load par_ser_red.gpr .

3) Run LVS.

4) Check the LVS result. The message netlists are topologically EQUIVALENT, and label mismatch is detected will be displayed.

5) Turn on the Parallel reduction and Series reduction options in the Models tab, and run LVS.

6) Check the LVS result. The message netlists are EQUIVALENT will be displayed.

par_mer_lvs.net

* Gateway 2.12.12.R Guardian Netlist Generator * Workspace name: /home/nobuhim/work/examples/Examples/lvs_example_04/demo.workspace * Simulation name: /home/nobuhim/work/examples/Examples/lvs_example_04/parallel_merge.schlr * Simulation timestamp: 28-Sep-2010 17:52:41 * Schematic name: parallel_merge .SUBCKT parallel_merge A Y M1 Y A VDD pmos L=0.4U W=2.4U M=1 M6 Y A GND nmos L=0.4U W=1.6U M=1 .ENDS parallel_merge * Global Nodes Declarations .GLOBAL GND * End of the netlist

par_mer_hier.spice

******************************************************************************* * * Extracted SPICE netlist for top cell parallel_merge * Created Tue Sep 28 17:54:50 2010 by hipex 3.4.7.R 64-bit (Tue May 25 12:44:06 PDT 2010) version * ******************************************************************************* .GLOBAL GND VDD .MODEL pmos PMOS .MODEL nmos NMOS ******************************************************************************* * * Sub-Circuit Netlist of : parallel_merge * ******************************************************************************* .subckt parallel_merge A Y GND VDD MI1 GND A Y GND nmos L=0.4U W=0.8U AS=0.64P AD=0.32P PS=3.2U PD=1.6U MI0 Y A GND GND nmos L=0.4U W=0.8U AS=0.32P AD=0.64P PS=1.6U PD=3.2U MI2 Y A VDD VDD pmos L=0.4U W=1.2U AS=0.48P AD=0.96P PS=2U PD=4U MI3 VDD A Y VDD pmos L=0.4U W=1.2U AS=0.96P AD=0.48P PS=4U PD=2U .ends parallel_merge .end

ser_mer_lvs.net

* Gateway 2.12.12.R Guardian Netlist Generator * Workspace name: /home/nobuhim/work/examples/Examples/lvs_example_04/demo.workspace * Simulation name: /home/nobuhim/work/examples/Examples/lvs_example_04/series_merge.schlr * Simulation timestamp: 28-Sep-2010 17:53:17 * Schematic name: series_merge .SUBCKT series_merge A Y M1 Y A VDD pmos L=0.8U W=2.4U M=1 M6 Y A GND nmos L=0.8U W=1.6U M=1 .ENDS series_merge * Global Nodes Declarations .GLOBAL GND * End of the netlist

ser_mer_hier.spice

******************************************************************************* * * Extracted SPICE netlist for top cell series_merge * Created Tue Sep 28 17:54:42 2010 by hipex 3.4.7.R 64-bit (Tue May 25 12:44:06 PDT 2010) version * ******************************************************************************* .GLOBAL GND VDD .MODEL pmos PMOS .MODEL nmos NMOS ******************************************************************************* * * Sub-Circuit Netlist of : series_merge * ******************************************************************************* .subckt series_merge A Y GND VDD MI1 #1 A Y GND nmos L=0.4U W=1.6U AS=1.28P AD=0.64P PS=4.8U PD=2.4U MI0 GND A #1 GND nmos L=0.4U W=1.6U AS=0.64P AD=1.28P PS=2.4U PD=4.8U MI2 VDD A #2 VDD pmos L=0.4U W=2.4U AS=0.96P AD=1.92P PS=3.2U PD=6.4U MI3 #2 A Y VDD pmos L=0.4U W=2.4U AS=1.92P AD=0.96P PS=6.4U PD=3.2U .ends series_merge .end

par_ser_red_lvs.net

* Gateway 2.12.12.R Guardian Netlist Generator * Workspace name: /home/nobuhim/work/examples/Examples/lvs_example_04/demo.workspace * Simulation name: /home/nobuhim/work/examples/Examples/lvs_example_04/parallel_series_reduction.schlr * Simulation timestamp: 28-Sep-2010 17:58:47 * Schematic name: parallel_series_reduction .SUBCKT parallel_series_reduction A B Y M1 Y A VDD pmos L=0.4U W=2.4U M=1 M2 Y B VDD pmos L=0.4U W=2.4U M=1 M5 Y B NET2 nmos L=0.4U W=1.6U M=1 M6 NET2 A GND nmos L=0.4U W=1.6U M=1 .ENDS parallel_series_reduction * Global Nodes Declarations .GLOBAL GND * End of the netlist

par_ser_red_hier.spice

******************************************************************************* * * Extracted SPICE netlist for top cell parallel_series_reduction * Created Tue Sep 28 17:54:59 2010 by hipex 3.4.7.R 64-bit (Tue May 25 12:44:06 PDT 2010) version * ******************************************************************************* .GLOBAL GND VDD .MODEL pmos PMOS .MODEL nmos NMOS ******************************************************************************* * * Sub-Circuit Netlist of : parallel_series_reduction * ******************************************************************************* .subckt parallel_series_reduction A B Y GND VDD MI1 #1 B GND GND nmos L=0.4U W=1.6U AS=1.28P AD=0.64P PS=4.8U PD=2.4U MI0 Y A #1 GND nmos L=0.4U W=1.6U AS=0.64P AD=1.28P PS=2.4U PD=4.8U MI2 Y A VDD VDD pmos L=0.4U W=2.4U AS=0.96P AD=1.92P PS=3.2U PD=6.4U MI3 VDD B Y VDD pmos L=0.4U W=2.4U AS=1.92P AD=0.96P PS=6.4U PD=3.2U .ends parallel_series_reduction .end