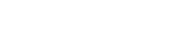

自動最適化

概要

CellForge 2D™ は、デジタル・スタンダード・セル・ライブラリの設計を単一のソリューションに集約し、自動化します。設計者は、ライブラリ内のすべてのセルの個々の属性を制御、変更することができ、厳しい設計要件にも対応できるよう、正確に調整することができます。CellForge 2D により、エンジニアは既存の作業を再利用して、トランジスタのサイジング、列の高さ、製造可能な設計ルール (DFM) などの設計パラメータを微調整し、消費電力、周波数、面積のトレードオフを管理することができます。さらに、CellForge 2D は、TCL を使用した包括的なレイアウト・カスタマイズ・スクリプト・インターフェイスを提供し、サードパーティ検証ツール(DRC、LVS、PEX)と最小限の影響で統合でき、レイアウト編集フロー内で柔軟に使用できます。

高度なレイアウト自動化フロー

- すべてのデザインルールに対応

- シングルハイトセルとダブルハイトセルの両方に対応

CellForge 2Dのフロー

特長

- プロセス技術とファウンドリのデザイン・ルールを迅速に設定し、使用開始から1週間程度でDRCによるクリーンなレイアウトを作成可能

- コンテキスト・センシティブなスペーシングおよびエンクロージャ・ルール、優先形状パターン、セルフ・アラインド・ダブル・パターニング(SADP)、ローカル・インタコネクトのサポートなど、高度なプロセス技術

- スループット向上のためのスケーラブルな並列処理

- 主要なサードパーティ製DRC、LVS、LPEツールとの統合により、高品質なサインオフ・レイアウトを実現し、お客様の既存フローへの影響を最小限に抑えることが可能

- GDSIIまたは、自動生成されたレイアウトから始まるフットプリント互換性のあるセルを生成し、きめ細かなドライブおよび多種におよぶスキューを考慮したセルを作成し、後工程でのスピードおよびパワーの最適化を実現

- Tclスクリプトのサポートにより、レイアウト・フローを柔軟にカスタマイズ可能

- Cadence Virtuoso プラグイン

利点

- 手作業によるレイアウト作業を排除または大幅に削減

- 生産性の大幅な向上

- さまざまな次元(セル・アーキテクチャ、設計ルール、サイジング戦略、DFMルール)での検討が可能

- セル・アーキテクチャ、テクノロジ・ノード、ファウンドリ間でレイアウトを移行可能

- ライブラリのポートフォリオを容易に拡張可能

- レイアウトの再利用

- インタラクティブなレイアウトのクリーンアップと最適化

- 構造化されたワークフロー:新規レイアウト・エンジニアのための最短2週間程度の立ち上げ期間