InVar IR-drop and Thermal Analysis

Silvaco’s InVar® performs IR-drop and thermal analysis on analog and mixed-signal IC designs.

Analysis of IR-drop and thermal effects have traditionally been a significant bottleneck in the physical verification of transistor level designs such as analog circuits, high-speed IOs, custom digital blocks, memories and standard cells. This is due to the need for accurate and increasingly complex analysis to be performed on designs that are progressively larger in size. For example, FinFET’s increased current density and thermal profile failure rate probabilities that must be managed with careful analysis and design.

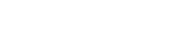

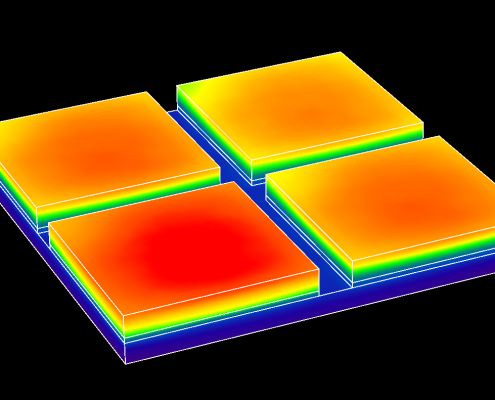

InVar’s hierarchical methodologies overcomes these hurdles and accurately models IR-Drop and thermal effects for designs ranging from single block to full-chip. Its patented concurrent electro-thermal analysis performs simulation of multiple physical processes together. InVar utilizes a true SPICE simulation engine, not simplified device models, for precision and applies parallel processing techniques to achieve performance. The result is physical measurement-like accuracy with high speed even on extremely large designs and applicability to all process nodes including FinFET technologies.

For a broad range of designs including processors, wired and wireless networks, sensors, high current ICs, sensors and displays, Silvaco’s InVar provides a user-friendly environment designed to assist quick turn-around-times and trouble free tape-outs.

Features

- Comprehensive IR-drop analysis gives full visibility of supply networks from top-level connectors down to each transistor. Hierarchical block modeling reduces runtime and memory and keeps accuracy of true flat run.

- Thermal analysis scales from single cell design to full chip and provides lab-verified accuracy of thermal analysis. Feedback from thermal engine to IR-drop engine ensures accuracy.

Benefits

- Accuracy verified in lab and foundries

- Full chip sign-off with accurate and high performance analysis

- Analysis available early in the back end design, when more design choices are available

- Pre-characterization not required for analysis

- Easy learning curve

- Broad range of technology nodes supported

Applications

- Analog and mixed-signal designs

Analog Custom Design Resources

Videos

News

Blogs

Customers

President and CEO

Using Viso to Investigate, Analyze, and Solve Complex Parasitic Issues

Power Devices SPICE Modeling for Si, GaN and SiC Technologies

Learn About Advanced TFT-Based Flat Panel Design with SmartSpice

Learn About the Latest Advances in Device Modeling Using Silvaco Utmost IV

Learn How Silvaco Flow Helps Designing and Simulating Pixel Arrays in Flat Panel Displays and Detectors